电子工程代写|超大规模集成电路系统代写Introduction to VLSI Systems代考|CSE435

如果你也在 怎样代写超大规模集成电路系统Introduction to VLSI Systems这个学科遇到相关的难题,请随时右上角联系我们的24/7代写客服。

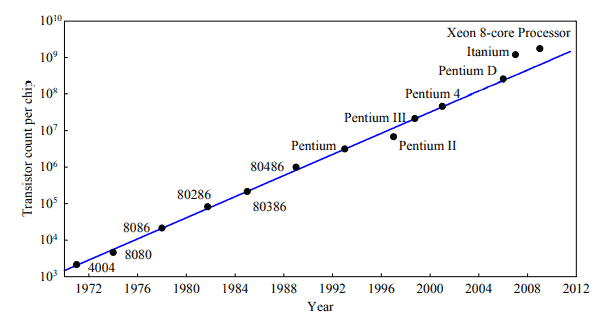

超大规模集成(VLSI)是通过将成千上万的晶体管合并到一个芯片中来创造集成电路(IC)的过程。VLSI开始于20世纪70年代,当时正在开发复杂的半导体和通信技术。微处理器就是一个VLSI设备。

statistics-lab™ 为您的留学生涯保驾护航 在代写超大规模集成电路系统Introduction to VLSI Systems方面已经树立了自己的口碑, 保证靠谱, 高质且原创的统计Statistics代写服务。我们的专家在代写超大规模集成电路系统Introduction to VLSI Systems方面经验极为丰富,各种代写超大规模集成电路系统Introduction to VLSI Systems相关的作业也就用不着说。

我们提供的超大规模集成电路系统Introduction to VLSI Systems及其相关学科的代写,服务范围广, 其中包括但不限于:

- Statistical Inference 统计推断

- Statistical Computing 统计计算

- Advanced Probability Theory 高等楖率论

- Advanced Mathematical Statistics 高等数理统计学

- (Generalized) Linear Models 广义线性模型

- Statistical Machine Learning 统计机器学习

- Longitudinal Data Analysis 纵向数据分析

- Foundations of Data Science 数据科学基础

电子工程代写|超大规模集成电路系统代写Introduction to VLSI Systems代考|CMOS Transmission Gates

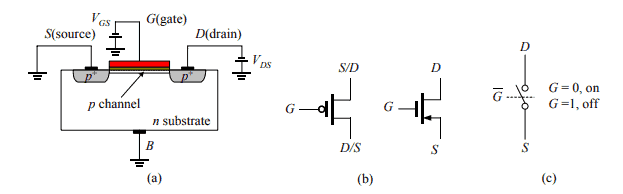

Since a voltage of magnitude $V_{T n}$ between the gate and source of an nMOS transistor is required to turn on the transistor, the maximum output voltage of an $n M O S$ switch is equal to $V_{D D}-V_{T n}$, provided that $V_{D D}$ is applied to both gate and drain electrodes. Similarly, the minimum output voltage of a pMOS switch is equal to $\left|V_{T p}\right|$, provided that $0 \mathrm{~V}$ is applied to both gate and drain electrodes. The above two statements can be restated in terms of information transfer by letting $0 \mathrm{~V}$ represent logic 0 and $V_{D D}$ denote logic 1 as follows. The nMOS transistor can pass 0 perfectly but cannot pass 1 without degradation; the pMOS transistor can pass 1 perfectly but cannot pass 0 without degradation.

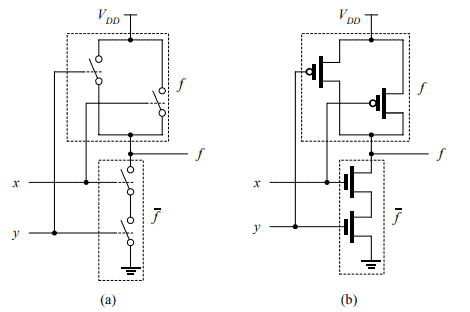

The aforementioned shortcomings of nMOS and pMOS transistors may be overcome by combining an nMOS transistor with a pMOS transistor as a parallel-connected switch, referred to as a transmission gate (TG) or a CMOS switch, as shown in Figure 1.9. Since both nMOS and pMOS transistors are connected in parallel, the imperfect feature of one transistor will be made up by the other. Figure $1.9(\mathrm{a})$ shows the circuit structure of a TG switch and Figure 1.9(b) shows the logic symbol often used in logic diagrams.

Even though using TG switches may overcome the degradation of information passing through them, each TG switch needs two transistors, one nMOS and one pMOS. This means that the use of TG switches needs more area than the use of nMOS switches or pMOS switches alone. In practice, for area-limited applications the use of nMOS transistors is much more prefcrable to pMOS transistors since the clectron mobility is much greater than hole mohility. Hence, nMOS transistors perform much hetter than pMOS transistors.

电子工程代写|超大规模集成电路系统代写Introduction to VLSI Systems代考|Simple Switch Logic Design

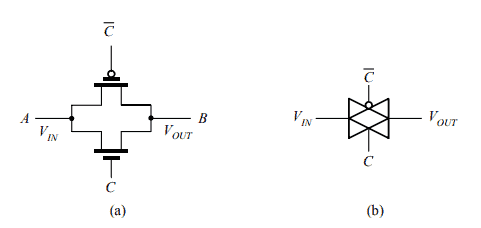

As introduced, any of three switches, nMOS, pMOS, and TG, may be used as a switch to control the close (on) or open (off) status of two points. Based on a proper combination of these switches, a switch logic circuit can be constructed. In the following, we begin with the discussion of compound switches and then introduce a systematic design methodology for constructing a switch logic circuit from a given switching function.

For many applications, we often combine two or more switches in a serial, parallel, or combined fashion to form a compound switch. For instance, the case of two switches being connected in series to form a compound switch is shown in Figure 1.10. The operation of the resulting switch is controlled by two control signals: $S 1$ and $S 2$. The compound switch is turned on only when both control signals $S 1$ and $S 2$ are asserted and remains in an off state otherwise.

Recall that to activate an nMOS switch we need to apply a high-level voltage to its gate and to activate a pMOS switch we need to apply a low-level voltage to its gate. As a result, the compound nMOS switch shown in Figure 1.10(a) is turned on only when both control signals $S 1$ and $S 2$ are at high-level voltages (usually $V_{D D}$ ) and remains in an off state in all other combinations of control signals. The compound pMOS switch depicted in Figure $1.10$ (b) is turned on only when both control signals $S 1$ and $S 2$ are at low-level voltages (usually at the ground level) and remains in an off state in all other combinations of control signals.

Figure $1.11$ shows the case of two switches being connected in parallel to form a compound switch. The operation of the resulting switch is controlled by two control signals: $S 1$ and $S 2$. The compound switch is turned on whenever either switch is on. Therefore, the compound switch is turned off only if both control signals $S 1$ and $S 2$ are deasserted and remains in an on state otherwise.

In Figure 1.11(a), the compound nMOS switch is turned on whenever one control signal of $S 1$ and $S 2$ is at a high-level voltage (usually $V_{D D}$ ) and remains in an off state only when both control signals are at the ground level. In Figure 1.11(b), the compound pMOS switch is turned on whenever one control signal of $S 1$ and $S 2$ is at the ground level and remains in an off state only when both control signals $S 1$ and $S 2$ are at high-level voltages.

超大规模集成电路系统代考

电子工程代写|超大规模集成电路系统代写Introduction to VLSI Systems代考|CMOS Transmission Gates

由于电压幅度在吨n一个nMOS晶体管的栅极和源极之间需要打开晶体管,一个的最大输出电压n米○小号开关等于在DD−在吨n, 前提是在DD应用于栅极和漏极。类似地,pMOS 开关的最小输出电压等于|在吨p|, 前提是0 在应用于栅极和漏极。上述两个陈述在信息传递方面可以通过让0 在表示逻辑 0 和在DD如下表示逻辑1。nMOS晶体管可以完美通过0但不能通过1而不退化;pMOS晶体管可以完美地通过1,但不能通过0而不退化。

上述 nMOS 和 pMOS 晶体管的缺点可以通过将 nMOS 晶体管与 pMOS 晶体管组合为并联开关(称为传输门 (TG) 或 CMOS 开关)来克服,如图 1.9 所示。由于nMOS和pMOS晶体管都是并联的,一个晶体管的不完善特性将由另一个晶体管来弥补。数字1.9(一个)图 1.9(b) 显示了 TG 开关的电路结构,图 1.9(b) 显示了逻辑图中常用的逻辑符号。

尽管使用 TG 开关可以克服通过它们的信息的劣化,但每个 TG 开关需要两个晶体管,一个 nMOS 和一个 pMOS。这意味着使用 TG 开关比单独使用 nMOS 开关或 pMOS 开关需要更多的面积。实际上,对于面积受限的应用,使用 nMOS 晶体管比使用 pMOS 晶体管更可取,因为电子迁移率远大于空穴迁移率。因此,nMOS 晶体管的性能比 pMOS 晶体管好得多。

电子工程代写|超大规模集成电路系统代写Introduction to VLSI Systems代考|Simple Switch Logic Design

如前所述,nMOS、pMOS和TG这三个开关中的任何一个都可以用作开关来控制两点的闭合(开)或开(关)状态。基于这些开关的适当组合,可以构建开关逻辑电路。下面,我们首先讨论复合开关,然后介绍一种系统设计方法,用于根据给定的开关功能构建开关逻辑电路。

对于许多应用,我们经常将两个或多个开关以串行、并行或组合的方式组合起来,形成一个复合开关。例如,两个开关串联形成复合开关的情况如图 1.10 所示。生成的开关的操作由两个控制信号控制:小号1和小号2. 只有当两个控制信号都打开复合开关小号1和小号2被断言并保持在关闭状态,否则。

回想一下,要激活 nMOS 开关,我们需要向其栅极施加高电平电压,而要激活 pMOS 开关,我们需要向其栅极施加低电平电压。结果,图 1.10(a) 所示的复合 nMOS 开关仅在两个控制信号小号1和小号2处于高电平电压(通常在DD) 并在所有其他控制信号组合中保持关闭状态。如图所示的复合 pMOS 开关1.10(b) 仅当两个控制信号都打开小号1和小号2处于低电平电压(通常处于地电平)并且在所有其他控制信号组合中保持关闭状态。

数字1.11显示了两个开关并联形成复合开关的情况。生成的开关的操作由两个控制信号控制:小号1和小号2. 只要任一开关打开,复合开关就会打开。因此,只有当两个控制信号都关闭复合开关小号1和小号2被置低,否则保持开启状态。

在图 1.11(a) 中,只要一个控制信号为小号1和小号2处于高电平电压(通常在DD) 并且仅当两个控制信号都处于地电平时才保持关闭状态。在图 1.11(b) 中,只要一个控制信号小号1和小号2处于地电平并且仅当两个控制信号都保持在关闭状态小号1和小号2处于高电平电压。

统计代写请认准statistics-lab™. statistics-lab™为您的留学生涯保驾护航。统计代写|python代写代考

随机过程代考

在概率论概念中,随机过程是随机变量的集合。 若一随机系统的样本点是随机函数,则称此函数为样本函数,这一随机系统全部样本函数的集合是一个随机过程。 实际应用中,样本函数的一般定义在时间域或者空间域。 随机过程的实例如股票和汇率的波动、语音信号、视频信号、体温的变化,随机运动如布朗运动、随机徘徊等等。

贝叶斯方法代考

贝叶斯统计概念及数据分析表示使用概率陈述回答有关未知参数的研究问题以及统计范式。后验分布包括关于参数的先验分布,和基于观测数据提供关于参数的信息似然模型。根据选择的先验分布和似然模型,后验分布可以解析或近似,例如,马尔科夫链蒙特卡罗 (MCMC) 方法之一。贝叶斯统计概念及数据分析使用后验分布来形成模型参数的各种摘要,包括点估计,如后验平均值、中位数、百分位数和称为可信区间的区间估计。此外,所有关于模型参数的统计检验都可以表示为基于估计后验分布的概率报表。

广义线性模型代考

广义线性模型(GLM)归属统计学领域,是一种应用灵活的线性回归模型。该模型允许因变量的偏差分布有除了正态分布之外的其它分布。

statistics-lab作为专业的留学生服务机构,多年来已为美国、英国、加拿大、澳洲等留学热门地的学生提供专业的学术服务,包括但不限于Essay代写,Assignment代写,Dissertation代写,Report代写,小组作业代写,Proposal代写,Paper代写,Presentation代写,计算机作业代写,论文修改和润色,网课代做,exam代考等等。写作范围涵盖高中,本科,研究生等海外留学全阶段,辐射金融,经济学,会计学,审计学,管理学等全球99%专业科目。写作团队既有专业英语母语作者,也有海外名校硕博留学生,每位写作老师都拥有过硬的语言能力,专业的学科背景和学术写作经验。我们承诺100%原创,100%专业,100%准时,100%满意。

机器学习代写

随着AI的大潮到来,Machine Learning逐渐成为一个新的学习热点。同时与传统CS相比,Machine Learning在其他领域也有着广泛的应用,因此这门学科成为不仅折磨CS专业同学的“小恶魔”,也是折磨生物、化学、统计等其他学科留学生的“大魔王”。学习Machine learning的一大绊脚石在于使用语言众多,跨学科范围广,所以学习起来尤其困难。但是不管你在学习Machine Learning时遇到任何难题,StudyGate专业导师团队都能为你轻松解决。

多元统计分析代考

基础数据: $N$ 个样本, $P$ 个变量数的单样本,组成的横列的数据表

变量定性: 分类和顺序;变量定量:数值

数学公式的角度分为: 因变量与自变量

时间序列分析代写

随机过程,是依赖于参数的一组随机变量的全体,参数通常是时间。 随机变量是随机现象的数量表现,其时间序列是一组按照时间发生先后顺序进行排列的数据点序列。通常一组时间序列的时间间隔为一恒定值(如1秒,5分钟,12小时,7天,1年),因此时间序列可以作为离散时间数据进行分析处理。研究时间序列数据的意义在于现实中,往往需要研究某个事物其随时间发展变化的规律。这就需要通过研究该事物过去发展的历史记录,以得到其自身发展的规律。

回归分析代写

多元回归分析渐进(Multiple Regression Analysis Asymptotics)属于计量经济学领域,主要是一种数学上的统计分析方法,可以分析复杂情况下各影响因素的数学关系,在自然科学、社会和经济学等多个领域内应用广泛。

MATLAB代写

MATLAB 是一种用于技术计算的高性能语言。它将计算、可视化和编程集成在一个易于使用的环境中,其中问题和解决方案以熟悉的数学符号表示。典型用途包括:数学和计算算法开发建模、仿真和原型制作数据分析、探索和可视化科学和工程图形应用程序开发,包括图形用户界面构建MATLAB 是一个交互式系统,其基本数据元素是一个不需要维度的数组。这使您可以解决许多技术计算问题,尤其是那些具有矩阵和向量公式的问题,而只需用 C 或 Fortran 等标量非交互式语言编写程序所需的时间的一小部分。MATLAB 名称代表矩阵实验室。MATLAB 最初的编写目的是提供对由 LINPACK 和 EISPACK 项目开发的矩阵软件的轻松访问,这两个项目共同代表了矩阵计算软件的最新技术。MATLAB 经过多年的发展,得到了许多用户的投入。在大学环境中,它是数学、工程和科学入门和高级课程的标准教学工具。在工业领域,MATLAB 是高效研究、开发和分析的首选工具。MATLAB 具有一系列称为工具箱的特定于应用程序的解决方案。对于大多数 MATLAB 用户来说非常重要,工具箱允许您学习和应用专业技术。工具箱是 MATLAB 函数(M 文件)的综合集合,可扩展 MATLAB 环境以解决特定类别的问题。可用工具箱的领域包括信号处理、控制系统、神经网络、模糊逻辑、小波、仿真等。